|     |     |        |                 |       |       |       |        |                   |        |               | Code No. : 2160                                                                                                         | 02  |

|-----|-----|--------|-----------------|-------|-------|-------|--------|-------------------|--------|---------------|-------------------------------------------------------------------------------------------------------------------------|-----|

| V   | A   |        |                 |       |       |       |        |                   |        |               | ING (Autonomous), HYDERABAD                                                                                             |     |

|     |     | M      | [.E. (          | ECI   | E: C  | BC    | S) I-  | Sem               | este   | r Ma          | nin Examinations, January-2018                                                                                          |     |

|     |     |        |                 |       |       | (E    | mbe    | dded              | Sys    | tems          | s & VLSI Design)                                                                                                        |     |

|     |     |        |                 |       |       |       |        | D                 | igita  | IIC           | Design                                                                                                                  |     |

| Tin | ne: | 3 ho   |                 | 4     | 4     |       |        | 4                 |        |               | Max. Marks: 60                                                                                                          |     |

|     |     |        | IVO             | ne: A | insu  | er A  |        | quest             | ions i | n Pa          | rt-A and any FIVE from Part-B                                                                                           |     |

|     |     |        |                 |       |       |       | 1      | Part-             | 4 (10  | $\times 2$    | = 20 Marks)                                                                                                             |     |

| 1.  | E   | xplai  | n MC            | SFE   | ET se | econ  | d ord  | ler ef            | fects. |               |                                                                                                                         |     |

| 2.  |     |        | ropag<br>n tech |       |       |       | of a C | CMOS              | Sinve  | erter         | modelled as a First-Order RC Network (Assume                                                                            |     |

| 3.  | E   | xplai  | n cha           | rge l | leaka | age p | orobl  | em ir             | dyn    | amic          | CMOS circuits.                                                                                                          |     |

| 4.  | Ir  | nplei  | nent -          | 4×1   | mux   | usi   | ng tr  | ansm              | issio  | n gat         | e logic.                                                                                                                |     |

| 5.  | C   | omp    | are Pl          | LL a  | nd I  | DLL   | in V   | LSIC              | Clock  | circ          | uits.                                                                                                                   |     |

| 6.  | D   | raw    | and e           | xpla  | in ci | rcuit | diag   | gram              | of Si  | mpli          | fied TSPC latch.                                                                                                        |     |

| 7.  | D   | )iscu: | ss des          | ign ( | chall | enge  | es in  | powe              | er dis | tribu         | tion in VLSI systems.                                                                                                   |     |

| 8.  | I   | mple   | ment            | 2 bit | con   | npara | ator 1 | using             | 1 bit  | com           | parator.                                                                                                                |     |

| 9.  | D   | )raw   | and e           | xpla  | in th | e cir | cuit   | diagr             | am o   | fa4           | T SRAM cell.                                                                                                            |     |

| 10. | E   | stim   | ate th          | e LE  | ofa   | a CM  | IOS I  | NAN               | D4.    |               |                                                                                                                         |     |

|     |     |        |                 |       |       |       |        | Part-             | -B (5  | × 8           | = 40 Marks)                                                                                                             |     |

| 11. | . a | ,      |                 |       |       |       |        |                   |        | is cl<br>+2.5 | t load of 3 pF: Compute the static and dynamic locked as fast as possible.  V $R_L = 75 \text{ k}\Omega$                | [5] |

|     |     |        | 1451            |       | ¥4    |       |        |                   |        | -             | V <sub>out</sub>                                                                                                        |     |

|     |     |        |                 |       |       |       |        | V <sub>an</sub> - |        | MI            | W/L = 1.5/0.5                                                                                                           |     |

|     |     |        |                 |       |       |       |        |                   |        | -             | Fig. 1                                                                                                                  |     |

|     | ł   |        | sume<br>e die y |       |       |       |        |                   |        |               | e of 2.5 cm <sup>2</sup> , 1 defects/cm <sup>2</sup> , and $\alpha$ =3. Determine                                       | [3] |

| 12  | . 8 | 0.2    | 25μm            | and   | 0.75  | μm/   | 0.25   | μm, r             | espec  | ctive         | assume NMOS and PMOS devices of $0.5 \mu m$ / ly. Find rise time and fall time this sizing should erise and fall times. | [5] |

|     | 1   | b) Im  | plem            | ent 2 | KOR   | and   | XN     | OR u              | sing   | Com           | plementary pass-transistor logic (CPL).                                                                                 | [3] |

13. a) Explain Design Techniques-dealing with Capacitive Cross Talk.

Estimate the Control voltage.

b) Implement a 200 MHz current starved ring oscillator using not more than 11 stages.

[3]

[5]

- 14. a) Implement a 16 bit Carry Save adder and estimate its propagation delay.

- [5]

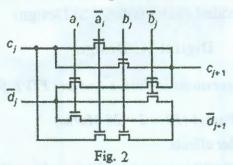

- b) Show how the arithmetic module in Figure 2 can be used as a comparator.

[3]

[5]

- 15. a) Estimate the word-line and bit-line capacitances of a 512 Kb SRAM arranged as a  $1024 \times 512$  array with access transistors of size  $(0.5\mu/0.1\mu)$ . Assume wire cap = 0.3 fF/ $\mu$ , bit line (contact) cap = 0.5 fF, Transistor D/S cap = Gate cap = 2 fF/ $\mu$ , and Cell size is  $50\lambda \times 40\lambda$ . Use  $0.13\mu$  technology and  $1\mu = 20\lambda$ .

- b) Explain write and read operations in a 3T DRAM cell. [3]

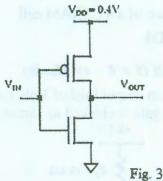

- 16. a) The inverter in Figure 3 operates with  $V_{DD}$ =0.4V and is composed of |Vt| = 0.5V devices. [5] The devices have identical  $I_0$  and n, calculate the switching threshold (VM) of this inverter.

- b) Draw the circuit diagram of four-input pseudo-NMOS NOR and NAND gates. [3]

- 17. Answer any two of the following:

- a) Explain the function of a 16 bit CSA. Estimate its t<sub>pd</sub>. [4]

- b) The layout of shifters is dominated by the number of wires running through a cell. For both the barrel shifter and the logarithmic shifter, estimate the width of a shifter cell as a function of the maximum shift-width M and the metal pitch p.

- c) Design a Row decoder to select one out of 16 bit lines based on address bits A3, A2, A1, and A0 and their complements. Compare its performance without a pre-decoder.

(अ(अ(अ))